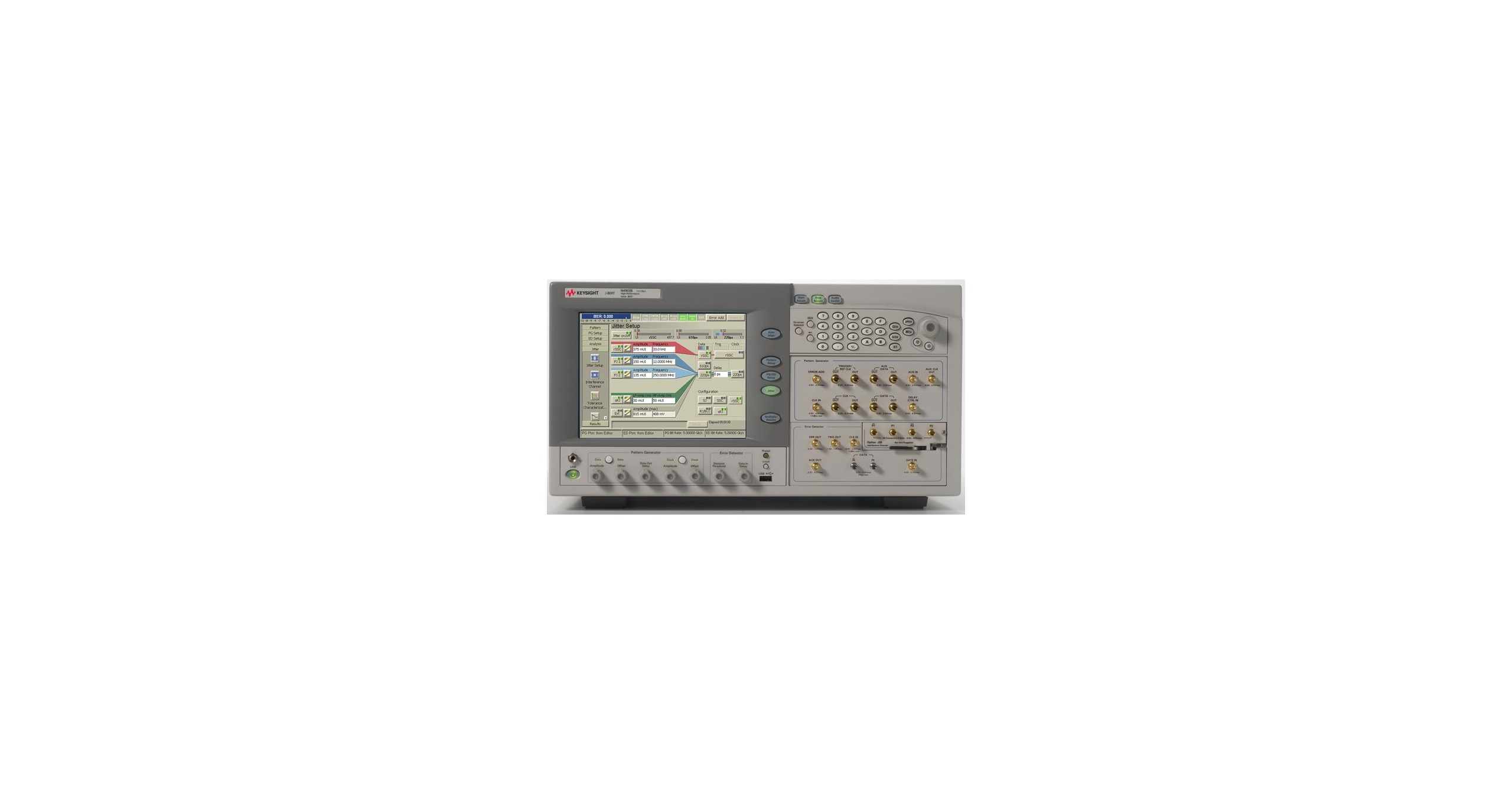

N4903B误码仪是德Keysight J-BERT 高性能串行 BERT

N4903B J-BERT 高性能串行 BERT,传输速率高达 7 Gb/s 和 12.5 Gb/s,具有完全的抖动容限

N4903B 是是德科技推出的一款高性能串行比特误码率测试仪。它不是一个通用的测量仪器,而是一个高度专业化的系统,主要用于测试和验证高速串行数据通信设备的性能,其核心是生成和分析极高速度的数字数据流,并计算误码率。

N4903B 关键属性详解

1. 测量范围

这里的“测量范围”主要指其工作的数据速率范围,这是BERT最核心的参数。

串行数据速率范围: 100 Mb/s 至 16 Gb/s(对于 NRZ 码型)这个范围覆盖了从传统通信协议到现代高速接口,如:

PCIe 1.0/2.0/3.0

光纤通道

10 Gigabit 以太网 / 10GBASE-KR

SATA / SAS

以及高达 16G 的各种自定义或专有协议。

2. 测量精度

对于BERT而言,“精度”主要体现在误码率测量、信号时序和信号完整性上:

误码率测量精度: BERT的误码率测量在统计上是绝对精确的。它通过直接对比发送和接收的比特数量来计算 BER。其置信度取决于捕获的总比特数和错误数。N4903B可以可靠地测量低至 10⁻¹² 甚至更低的误码率。

输出抖动: 极低,典型值 < 1 ps RMS。这是保证输出信号质量的关键。

时序调谐精度: 其内置的误码检测器具有精密的延迟扫描功能,可以精确测量被测设备的眼图张开度和抖动容限,精度在 ps 量级。

3. 电源电压

供电要求: 使用标准的交流电源。

电压: 100 - 240 VAC,自动适应。

频率: 50/60 Hz。

功耗: 最大约 350 瓦。

根据配置和负载情况,功耗会有所不同。

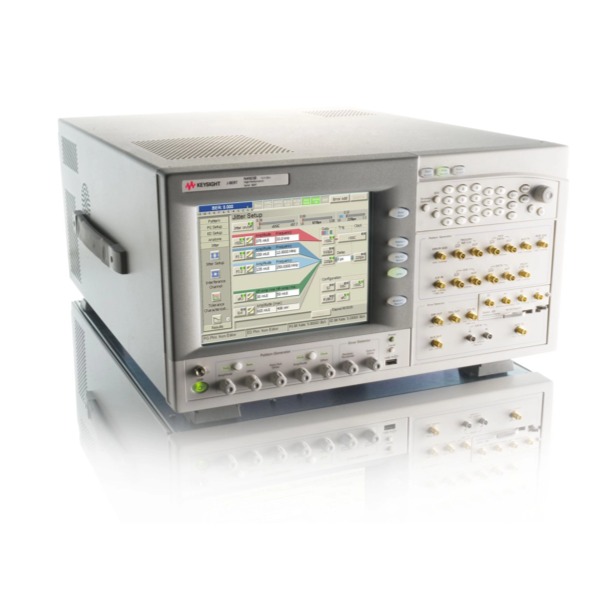

4. 尺寸与重量

N4903B采用是德科技模块化仪器的主流平台(与M9500A等主机类似)的物理规格。

外形尺寸(宽 × 高 × 深):426 mm × 177 mm × 500 mm(16.8 in × 7.0 in × 19.7 in)

格式: 标准的半机架宽度和3U高度设计,非常适合集成到测试机柜中。

重量: 约 17 kg。

5. 用途

N4903B的应用非常专注于高速数字和光通信领域的研发、验证和一致性测试。

研发与验证:

集成电路测试: 测试SerDes(串行器/解串器)PHY芯片的接收器抖动容限和发送器眼图质量。

光模块测试: 测试SFP+, SFP28, QSFP+等光收发模块的误码性能。

系统板卡测试: 测试交换机、路由器、服务器主板上的高速串行链路。

一致性测试:

提供各种一致性测试软件(如用于PCIe, Fibre Channel等),自动化地执行标准规定的测试套件,判断设备是否符合规范。

极限测试:

通过在其输出的数据流中添加可控的抖动和噪声,来测试接收端在最恶劣情况下的性能,即压力眼测试。

核心用途 高速SerDes、光模块、交换机/路由器板卡的误码率测试、接收机容限测试和一致性测试

重要提示:

以上规格为基于公开资料的典型值。N4903B是一个可配置的系统,其精确规格(如支持的接口类型、是否需要时钟恢复模块等)取决于具体配置。在进行任何设计或采购决策前,请务必查阅 Keysight官方发布的N4903B数据手册、配置指南和用户手册,以获取最准确、最完整的信息。

概述和功能

数据速率为 150 Mb/s 至 7 Gb/s,或最高可达 12.5 Gb/s 的模式生成器和错误检测器。模式生成器可选扩展数据速率至 14.2 Gb/s。

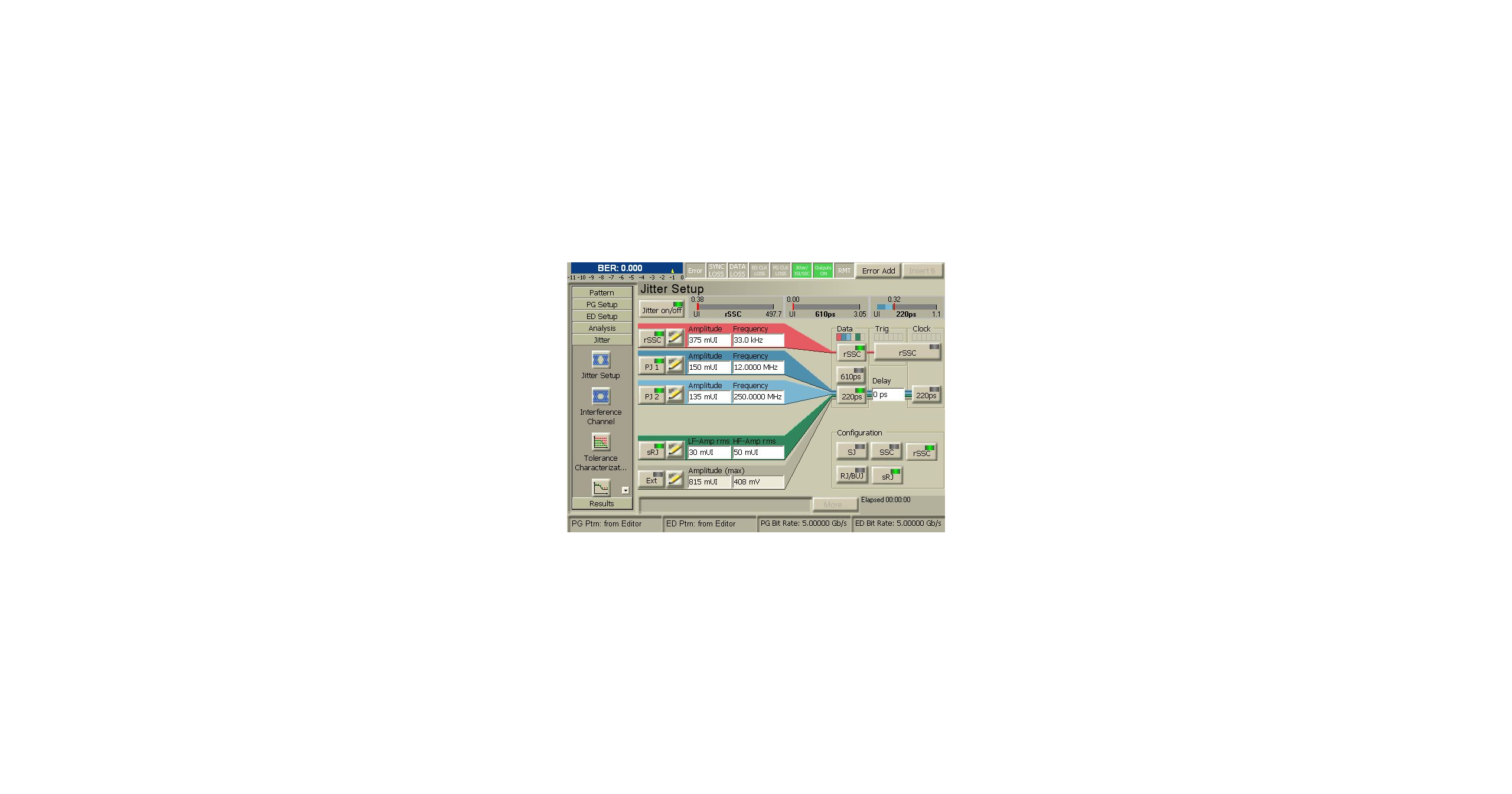

>0.5 UI 校准、合规且集成的抖动注入:RJ、RJ-LF、RJ-HF、PJ1、PJ2、SJ、BUJ、ISI、正弦干扰、三角波和任意 SSC 以及残余 SSC

优异的信号性能和灵敏度

内置时钟数据恢复功能,具有可调且兼容的环路带宽

适用于前馈时钟器件的半速率时钟,具有可变占空比

测量误码率 (BER)、误码率扫描、带 RJ/DJ 分离的 TJ、眼图、眼图掩模、BER 轮廓、自动抖动容限、模式捕获、帧错误率 (FER) 或符号错误率 (SER) 编码和重定时数据流

两个可调数据输出,带有独立的伪随机二进制序列 (PRBS) 和模式,以及 120 块模式序列器

所有选项均可进行改装,并可从 N4903A 升级。

J -BERT N4903B 高性能串行 BERT为嵌入式和前向时钟设备提供最完整的抖动容限测试。

对于研发和验证团队而言,它是表征和测试具有高达 7 Gb/s、12.5 Gb/s 或 14.2 Gb/s 串行 I/O 端口的芯片和收发器模块的理想选择。它可以表征接收器的抖动容限,并旨在验证其是否符合当今最流行的串行总线标准,例如:

PCI Express®测量解决方案示例:PCIe 3.0 接收器测试

SATA/SAS

DisplayPort

USB 超高速

光纤通道

QPI

内存总线,例如全缓冲 DIMM2

背板,例如 CEI

10 GbE/ XAUI

XFP/XFI、SFP+

J-BERT N4903B 的主要优势:

利用来自信号发生器的纯净信号可以实现精确的特性分析,该信号发生器具有极低的抖动和极快的转换时间。内置的校准抖动源可以对接收机进行精确的抖动容限测试。

由于 J-BERT N4903B 的设计与串行总线标准完美匹配,其差分 I/O、大多数输出端的可变电压电平、内置抖动和 ISI 检测、模式序列器、参考时钟输出、可调 CDR、模式捕获和位恢复模式可分析无时钟和非确定性模式,因此测试设置显著简化。SER/FER 分析允许使用重定时环回对器件进行抖动容限测试。第二个数据输出具有独立的模式存储器和 PRBS,可用作串扰测试的干扰通道,或在外部添加通道进行带外 (OOB) 定时测试、模拟三电平信号或信号去加重时使用。

J-BERT 的自动抖动容限测试可快速进行总抖动测量,从而加快测试执行速度。

J-BERT N4903B 是一项长期投资,它可根据当今的测试和预算要求进行配置,同时还允许从 N4903A 型号升级,并在测试需求发生变化时,以后可以对所有选项和全速进行改造。